Cómo avanza ZK Proof Startup Cysic en la hoja de ruta de aceleración de hardware de ZK

Puntos claves:

- Cysic, una startup de hardware de conocimiento cero, completó recientemente una ronda de financiación inicial de 6 millones de dólares liderada por Polychain Capital.

- El objetivo principal de Cysic es proporcionar servicios acelerados por hardware para el proceso de generación de pruebas ZK del proyecto ZK.

- Cysic ya ha alcanzado su intención de asociarse con algunos de los proyectos líderes de ZK y primero proporcionará servicios de aceleración de MSM para estos proyectos.

Cysic es un proyecto de aceleración de hardware ZK líder en la industria dedicado al diseño de chips ASIC avanzados para ayudar a reducir el tiempo de generación a prueba de ZK. Cysic ha formado un equipo de diseño y desarrollo de hardware de primera clase y ha completado el trabajo de diseño de POC basado en FPGA.

Según los resultados de POC, se puede demostrar que la capacidad de aceleración de hardware ZK de Cysic ya se encuentra en una posición líder en la industria.

ABCDE invirtió en Cysic en la ronda inicial, y las instituciones de inversión en esta ronda también incluyen Polychain, A&T, Hashkey y Web3.com Venture.

¿Por qué necesitamos la aceleración de hardware ZK?

La generación de prueba ZK (ZK Proof Generation) es uno de los pasos centrales del proyecto ZK. Desafortunadamente, bajo los sistemas de prueba ZK existentes, generar pruebas ZK generalmente requiere muchos cálculos. A medida que aumenta la complejidad del proyecto y aumenta la escala del circuito ZK, la cantidad de cálculo requerido para la generación de pruebas ZK aumentará exponencialmente.

Por ejemplo, para proyectos zkEVM/zkVM a gran escala como Scroll y zkSync, pueden llevar horas o incluso días de cálculo si se utiliza la CPU para generar pruebas ZK. En los negocios reales, la mayoría de los proyectos necesitan limitar la generación de pruebas ZK a segundos y minutos. Un tiempo de cálculo de varias horas o más es completamente inaceptable para la mayoría de los proyectos ZK, especialmente para proyectos de expansión como zkEVM/zkVM.

Además, la complejidad computacional de la generación de pruebas ZK es difícil de reducir teóricamente en el período de aproximadamente dos años antes del lanzamiento oficial del proyecto ZK en el futuro.

Por lo tanto, para garantizar la usabilidad del proyecto, antes de que se lance oficialmente, la parte del proyecto ZK debe adoptar la solución técnica de "acelerar la generación de pruebas ZK" para acelerar la generación de pruebas ZK al nivel segundo o minuto. . El método de acelerar la generación a prueba de ZK mediante hardware de alto rendimiento es actualmente la primera opción.

¿Qué es la aceleración por hardware?

En el proceso de generación de pruebas ZK, los principales cálculos que requieren mucho tiempo se pueden dividir en dos tipos:

1. Cálculo de NTT (Transformación Teórica de Números) basado en polinomios

2. Cálculos MSM (Multiplicación Multiescalar) sobre curvas elípticas. En términos generales, en un cálculo generado por una prueba ZK, las tareas informáticas de tipo NTT representan aproximadamente el 25% de todas las tareas informáticas, y las tareas informáticas de tipo MSM representan aproximadamente el 60-70%.

Afortunadamente, existen estos dos tipos de tareas informáticas:

1. La lógica es relativamente simple.

2. Una gran cantidad de repeticiones de la misma lógica informática.

3. Las características del paralelismo (similar a la computación de Bitcoin Mining). Por tanto, es teóricamente factible utilizar hardware de alto rendimiento para acelerar estos dos tipos de cálculos.

Como se muestra en la figura siguiente, podemos encontrar que el cálculo NTT (parte superior izquierda) y el cálculo MSM (lado derecho) están ligeramente acoplados en el flujo de trabajo de generación de pruebas ZK. Por lo tanto, el grupo del proyecto ZK puede elegir según las necesidades reales:

1. Acelere el cálculo de NTT solo o

2. Acelere el cálculo de MSM solo

3. Acelerar NTT y MSM en su conjunto, tres opciones.

Flujo de trabajo del proceso de generación de pruebas generales ZK

- Nota 1: La imagen de arriba es del artículo del cofundador de Scroll, Zhang Ye: PipeZK: Accelerating Zero-Knowledge Proof with a Pipelined Architecture. Este es uno de los primeros artículos de la industria que estudia la aceleración de hardware zk.

- Nota 2: En alguna literatura/artículos, se afirma que la generación de pruebas ZK que consume más tiempo es FFT (Transformada Rápida de Fourier) y MSM. Aunque los principios de FFT y NTT son similares, dado que la mayoría de los cálculos criptográficos involucrados en ZK se realizan en campos finitos (campo finito), el cálculo real debería ser NTT. Por lo tanto, tomamos como estándar el NTT utilizado en la mayoría de los artículos académicos.

¿Para qué se utiliza la aceleración de hardware?

De manera similar a la solución de minería, la solución actual de aceleración de hardware de ZK se implementa principalmente a través de los siguientes tres tipos de hardware:

- GPU

- FPGA

- ASIC

Actualmente, existen dos soluciones principales de aceleración de hardware disponibles en el mercado: GPU y FPGA. Los esquemas de aceleración que utilizan GPU/FPGA son relativamente fáciles de implementar. Por lo tanto, para conquistar el mercado más rápido, la mayoría de los fabricantes implementarán primero la solución GPU/FPGA. Debido al alto costo del hardware de las GPU y FPGA, el consumo de energía relativamente alto y el rendimiento absoluto limitado. Por tanto, la solución ASIC es una parte que no se puede ignorar en el ecosistema de aceleración de hardware de ZK.

Cómo la aceleración de hardware beneficia al grupo del proyecto ZK

Los proveedores de aceleración de hardware ZK pueden proporcionar servicios de aceleración de generación a prueba de ZK de dos maneras:

- A través de API SaaS.

- Proporcionar servicios de aceleración (similares a la venta de máquinas mineras) mediante la venta de hardware (máquina completa/chip).

Como mencionamos anteriormente, durante la generación de pruebas ZK, los cálculos de NTT y MSM están ligeramente acoplados. Por lo tanto, según las diferentes granularidades del servicio, los proveedores de servicios de aceleración de hardware pueden proporcionar los siguientes tres servicios granulares.

- Aceleración NTT dedicada (API de aceleración NTT dedicada/dispositivo de hardware)

- Aceleración MSM dedicada (API/dispositivo de hardware de aceleración MSM dedicada)

- Solución de aceleración todo en uno para acelerar NTT y MSM al mismo tiempo.

Diferencias en los proveedores de aceleración de hardware

Los problemas informáticos de NTT y MSM se han estudiado exhaustivamente durante muchos años. Es difícil para los principales fabricantes lograr avances en la teoría de la computación en un corto período de tiempo. Por lo tanto, las diferencias técnicas entre varios fabricantes radican más en las capacidades de realización de ingeniería, el control de los detalles del algoritmo, la selección de la pila de tecnología (hardware), el control de costos de producción de hardware y las capacidades de diseño de productos. Cuando los clientes eligen un proveedor de aceleración, se centrarán en los tres factores siguientes:

- El rendimiento del hardware/servicio y el tiempo de computación del fabricante bajo la misma tarea informática.

- El costo de aceleración del hardware, bajo la misma tarea informática, es el costo informático del fabricante.

- Facilidad de uso de la API/dispositivo.

¿Por qué invertimos en Cysic?

Cysic fue fundada a finales de agosto de 2022 por Leo Fan y Bowen Huang. El objetivo principal de Cysic es proporcionar servicios de aceleración de hardware para el proceso de generación a prueba de ZK del proyecto ZK. California, Estados Unidos y China continental. Los antecedentes de estos miembros fundadores provienen principalmente de doctores del Departamento de Ciencias de la Computación de las 20 mejores universidades de los Estados Unidos y del equipo de diseño de chips del Instituto de Tecnología Informática de la Academia de Ciencias de China.

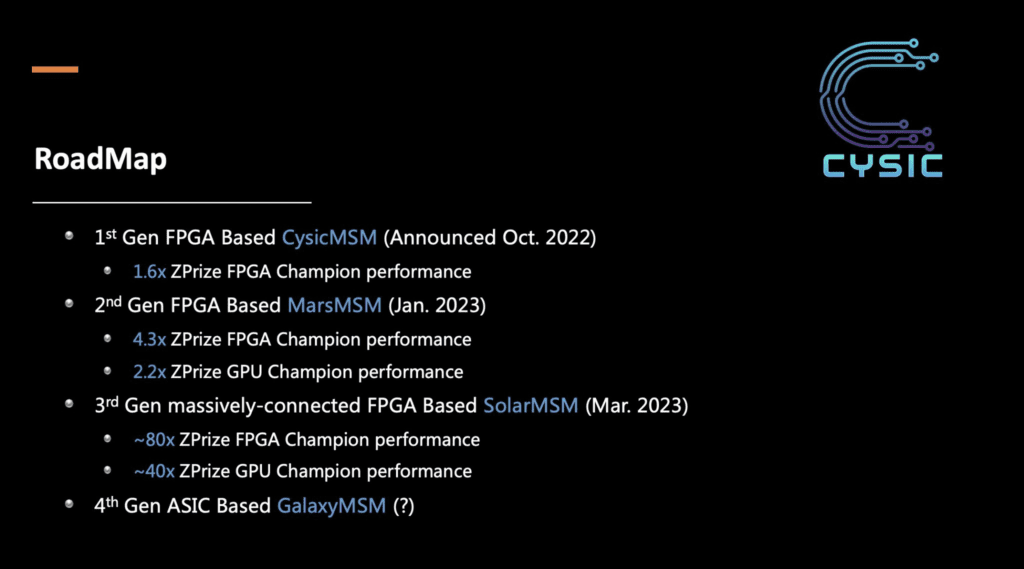

En esta etapa, el proyecto ha realizado la verificación POC del cálculo MSM basado en FPGA y el código del proyecto es SolarMSM. En esta etapa, SolarMSM proporcionará servicios externos a través de SaaS.

En la actualidad, Cysic ha alcanzado intenciones de cooperación con varios de los principales participantes del proyecto ZK y les proporcionará servicios de prueba en un futuro próximo. Según la evidencia de muchas autoridades de la industria, SolarMSM se encuentra en la posición de primer nivel en la industria en aceleración del rendimiento informático de MSM.

Perfil del equipo fundador

Los dos fundadores tienen una sólida formación técnica y son expertos en criptografía y diseño de hardware. El Dr. Leo se graduó de la Universidad de Cornell bajo la tutela de una profesora de criptografía de renombre internacional, Elaine Shi. Antes de unirse a la Universidad de Rutgers como profesor asistente, Leo trabajó como investigador de criptografía en Algorand.

Otro fundador, Bowen Huang, trabajó en el Instituto de Tecnología Informática de la Academia de Ciencias de China durante 6 años antes de fundar Cysic e ir a la Universidad de Yale para estudiar un doctorado. Aterrizaje de diseño.

Resultados del POC

En la actualidad, Cysic ha implementado el diseño POC de la solución de aceleración MSM basada en la FPGA pública de Xilinx, cuyo nombre en código es SolarMSM. En la verificación POC, para la tarea informática MSM cuyo tamaño de entrada es 2³⁰, SolarMSM puede acelerarla a menos de un segundo. Actualmente, este es el nivel más sólido entre todos los resultados de datos públicos de la industria y es entre 1 y 2 órdenes de magnitud mayor que el desempeño del campeón de la competencia ZPrize.

La rápida implementación de SolarMSM demuestra:

- El equipo de Cysic tiene capacidades técnicas y de I+D eficientes. Se puede diseñar e implementar rápidamente, lo que es entre 1 y 2 órdenes de magnitud mayor que el primer ZPrize, lo que muestra una ventaja de velocidad abrumadora.

- El equipo de Cysic tiene una sólida capacidad de gestión de integración de la cadena de suministro. Si la PCB, la disipación de calor, la fuente de alimentación, los conectores PCIE y la estructura del chasis se personalizan en paralelo, la entrega aún se puede completar rápidamente en 2 o 3 meses, lo que es básicamente 2 o 3 veces la velocidad del estándar de la industria.

Al mismo tiempo, la POC en esta etapa también es una verificación interna del trabajo de diseño/desarrollo del hardware de Cysic. Debido a que el costo de corrección de errores de los chips ASIC es mayor que el de las soluciones FPGA, la verificación completa de la máquina a través de SolarMSM con un gran ancho de banda, un alto consumo de energía y altos niveles de interconexión puede reducir en gran medida el riesgo de errores futuros en los chips ASIC.

Hoja de ruta tecnológica

Cysic planea proporcionar una solución completa de aceleración de hardware ASIC, incluida la informática NTT y MSM. Actualmente, el grupo del proyecto adopta una estrategia de I+D en dos etapas.

Fase 1: POC basada en FPGA

En la primera fase del proyecto, se desarrolló una versión POC de MSM y aceleración NTT basada en la FPGA pública de Xilinx: SolarMSM. En la actualidad, se ha completado el módulo de aceleración informática MSM y la informática MSM de escala 2³⁰ se puede completar en menos de un segundo, que es el rendimiento más alto entre todos los resultados públicos de aceleración de hardware FPGA-MSM, liderando la competencia por más de 1-2 órdenes de magnitud. Al menos, SolarMSM mantendrá el récord de rendimiento más alto para la aceleración de hardware MSM hasta que salgan los chips ASIC. Cysic ha alcanzado intenciones de cooperación con varios proyectos líderes de ZK y primero proporcionará servicios de aceleración de MSM para estos proyectos.

En los próximos meses, Cysic planea completar el módulo de aceleración informática NTT SolarNTT basado en SolarMSM. SolarNTT y SolarMSM se implementarán en el mismo servidor para realizar computación acelerada basada en el mismo sistema de interconexión FPGA a gran escala. Estos dos conjuntos de implementaciones se integrarán a través de la arquitectura de interconexión de alta velocidad diseñada por Cysic para convertirse en una solución de aceleración todo en uno, SolarZKP. SolarZKP proporcionará servicios API de forma externa a través de SaaS.

Fase 2: ASIC de 12 nm

Después de la etapa POC, Cysic comenzará la etapa de desarrollo ASIC de 12 nm. El objetivo es lograr que la potencia informática de un único chip ASIC alcance el rendimiento de todo el SolarZKP (que admita la informática MSM y NTT y otras funciones centrales especificadas por la parte del proyecto) y, al mismo tiempo, reducir el consumo de energía de un solo chip a dos órdenes de magnitud.

Análisis de mercado

¿Cómo eligen los clientes las soluciones de aceleración de hardware??

En la producción real, diferentes clientes de ZK tienen diferentes requisitos de aceleración de hardware, dependiendo de qué tan sensible sea el proyecto ZK al tiempo de generación de la prueba. Por ejemplo:

- Para proyectos de Capa 2 basados en zkEVM/zkVM, su requisito principal es la generación rápida y estable de pruebas ZK. Por lo tanto, estarán más inclinados a elegir una solución de aceleración integrada más rápida y estable.

- Para algunos proyectos ZK que no son sensibles al tiempo de generación de pruebas ZK, no necesitan generar pruebas a la velocidad más rápida, como las pruebas de propiedad de los intercambios. En este escenario, los clientes pueden elegir de manera flexible la aceleración informática MSM sola o combinar la informática MSM y la informática NTT proporcionadas por diferentes proveedores de servicios dentro de un tiempo aceptable para elegir el mejor precio.

Creemos que en el futuro habrá herramientas que combinen las soluciones de diferentes proveedores de aceleración de hardware para ayudar a los clientes a generar soluciones óptimas.

Riesgo del proyecto

En la actualidad, muchas empresas han participado en la competencia en la pista acelerada por hardware ZK. Existen riesgos de retraso en el desarrollo de proyectos y riesgos de mercado para los proyectos de aceleración de hardware ZK basados en ASIC.

Riesgo de retraso en el desarrollo del proyecto

Existe una relación de cooperación mutua y logros mutuos entre la parte del proyecto ZK y el fabricante de aceleración de hardware ZK. Como parte del proyecto ZK, primero elegirá la primera solución de aceleración de hardware disponible para aprovechar la participación de mercado del propio proyecto ZK. Para el proyecto zkEVM/zkVM, poder proporcionar pruebas de bloque L2 de manera estable es una de las consideraciones más importantes. Por lo tanto, algunas partes del proyecto ZK alcanzarán intenciones de cooperación a largo plazo con proveedores de aceleración de hardware en la etapa inicial. Si el desarrollo del proyecto es demasiado lento, parte de la cuota de mercado puede perderse en la fase inicial. Al mismo tiempo, existe el riesgo de fallo en la cinta de salida del ASIC. Afectados por las limitaciones de capacidad de los fabricantes de chips, las fallas en la cinta de salida obligarán al proyecto a reprogramar la cinta de salida, lo que provocará retrasos en el proyecto.

Riesgo de mercado

El grupo del proyecto ZK se puede dividir en dos categorías: la categoría de privacidad y la categoría de expansión. Para proyectos de privacidad, el uso de la aceleración de hardware puede reducir el riesgo de ataques de canal lateral hasta cierto punto, pero considerando los problemas de privacidad, los proyectos de privacidad serán más cautelosos al elegir las soluciones de aceleración de hardware de ZK, como elegir comprar hardware directamente en lugar de no a través de SaaS. servicio.

Competición de jefes de proyecto

En la actualidad, existen tres competidores poderosos en la industria: Supranational, Ulvantanna y Auradine.

Supranacional

Supranational ha entrado en la pista ZK acelerada por GPU desde 2019 y recientemente comenzó a involucrarse en el campo FPGA/ASIC. Supranational ya tiene una solución de aceleración basada en GPU de código abierto muy madura y su rendimiento está a la vanguardia de la industria. Al mismo tiempo, esperamos que Supranational también tenga una solución comercial de código cerrado con mejor rendimiento. Supranational entró al mercado antes, con ciertos recursos industriales y un buen flujo de caja.

Ulvantana

El equipo fundador es de Jump Crypto y ha recibido inversiones de paradigm y bain crypto. No se debe subestimar su fuerza.

auradina

En comparación con Senior, el equipo fundador tiene una rica experiencia empresarial y una plataforma de los mejores fabricantes y capital.

Otros equipos de aceleración de hardware

El resto de equipos, como Ingonyama y Jump Crypto, entraron a la pista antes que ellos, pero su desempeño no es tan bueno como el de SolarMSM a estas alturas, según los datos públicos.

Equipo interno de aceleración de hardware del proyecto ZK.

En la actualidad, además de los equipos dedicados a la aceleración de hardware, muchas partes del proyecto ZK también están explorando internamente soluciones de aceleración de hardware, como zkSync y Scroll.

zkSync

zkSync elige la solución de aceleración GPU/FPGA. Según los resultados publicados en ZPrice, la solución GPU de zkSync tarda 2.528 segundos cuando la escala de entrada es 2²⁶ MSM. Este rendimiento es menos de una décima parte de la solución Cysic SolarMSM (el cálculo de 2³⁰ MSM tarda menos de 1 segundo).

Voluta

Voluta ha sido investigado internamente para la aceleración basada en GPU. Al mismo tiempo, Scroll y algunas instituciones académicas están cooperando para explorar mejores soluciones, y los resultados de sus últimas investigaciones académicas se publicaron en ASPLOS 2023, la conferencia más importante en el campo de la arquitectura informática [3]. Como proyecto líder de zkEVM, vale la pena esperar y seguir su progreso de seguimiento.

Referencias

[1] PipeZK: Aceleración de la prueba de conocimiento cero con una arquitectura canalizada, ZhangYe [2] Aceleración FPGA de multiplicación multiescalar: CycloneMSM, JumpCrypto [3] GZKP: un sistema de prueba de conocimiento cero acelerado por GPUEXENCIÓN DE RESPONSABILIDADES: La información de este sitio web se proporciona como un comentario general del mercado y no constituye un consejo de inversión. Le animamos a que haga su propia investigación antes de invertir.

Únase a nosotros para estar al tanto de las novedades: https://linktr.ee/coincu

Harold

Coincú Noticias