ZK हार्डवेयर एक्सेलेरेशन रोडमैप में ZK प्रूफ स्टार्टअप सिसिक ब्रेकथ्रू कैसे हुआ

प्रमुख बिंदु:

- साइसिक, एक शून्य-ज्ञान हार्डवेयर स्टार्टअप, ने हाल ही में पॉलीचैन कैपिटल के नेतृत्व में $6 मिलियन का सीड फंडिंग राउंड पूरा किया है।

- Cysic का प्राथमिक लक्ष्य ZK प्रोजेक्ट की ZK प्रूफ-जनरेशन प्रक्रिया के लिए हार्डवेयर-त्वरित सेवाएं प्रदान करना है।

- Cysic पहले ही कुछ प्रमुख ZK परियोजनाओं के साथ साझेदारी करने के अपने इरादे पर पहुँच चुका है और सबसे पहले इन परियोजनाओं के लिए MSM त्वरण सेवाएँ प्रदान करेगा।

Cysic एक उद्योग-अग्रणी ZK हार्डवेयर त्वरण परियोजना है जो ZK-प्रूफ पीढ़ी के समय को कम करने में मदद करने के लिए उन्नत ASIC चिप्स को डिजाइन करने के लिए समर्पित है। Cysic ने एक प्रथम श्रेणी हार्डवेयर डिज़ाइन और विकास टीम का गठन किया है और FPGA-आधारित POC डिज़ाइन कार्य पूरा कर लिया है।

POC परिणामों के अनुसार, यह साबित किया जा सकता है कि Cysic की ZK हार्डवेयर त्वरण क्षमता पहले से ही उद्योग में अग्रणी स्थिति में है।

एबीसीडीई ने सीड राउंड में सिसिक में निवेश किया और इस राउंड में निवेश संस्थानों में पॉलीचेन, ए एंड टी, हैशकी और वेब3.कॉम वेंचर भी शामिल हैं।

हमें ZK हार्डवेयर त्वरण की आवश्यकता क्यों है?

ZK प्रूफ़ की पीढ़ी (ZK प्रूफ़ जेनरेशन) ZK परियोजना के मुख्य चरणों में से एक है। दुर्भाग्य से, मौजूदा ZK प्रूफ सिस्टम के तहत, ZK प्रूफ तैयार करने के लिए आमतौर पर बहुत अधिक गणना की आवश्यकता होती है। जैसे-जैसे परियोजना की जटिलता बढ़ती है और ZK सर्किट का पैमाना बढ़ता है, ZK प्रूफ पीढ़ी के लिए आवश्यक गणना की मात्रा तेजी से बढ़ेगी।

उदाहरण के लिए, बड़े पैमाने पर zkEVM/zkVM परियोजनाओं जैसे स्क्रॉल और zkSync के लिए, यदि यह ZK प्रमाण उत्पन्न करने के लिए CPU का उपयोग करता है तो गणना में घंटों या यहां तक कि दिन भी लग सकते हैं। वास्तविक व्यवसाय में, अधिकांश परियोजनाओं को ZK प्रमाणों की पीढ़ी को सेकंड और मिनटों तक सीमित करने की आवश्यकता होती है। अधिकांश ZK परियोजनाओं के लिए कई घंटों या उससे अधिक का कंप्यूटिंग समय पूरी तरह से अस्वीकार्य है, विशेष रूप से zkEVM/zkVM जैसी विस्तार परियोजनाओं के लिए।

इसके अलावा, भविष्य में ZK परियोजना के आधिकारिक तौर पर लॉन्च होने से पहले लगभग दो साल की समय सीमा में ZK प्रूफ पीढ़ी की कम्प्यूटेशनल जटिलता को सैद्धांतिक रूप से कम करना मुश्किल है।

इसलिए, परियोजना की उपयोगिता सुनिश्चित करने के लिए, परियोजना के आधिकारिक तौर पर लॉन्च होने से पहले, ZK परियोजना पार्टी को ZK प्रमाणों की पीढ़ी को दूसरे या मिनट के स्तर तक तेज करने के लिए "ZK प्रमाणों की पीढ़ी में तेजी लाने" के तकनीकी समाधान को अपनाना होगा। . उच्च-प्रदर्शन हार्डवेयर के माध्यम से ZK-प्रूफ पीढ़ी को तेज करने की विधि वर्तमान में पहली पसंद है।

हार्डवेयर त्वरित क्या है?

ZK प्रूफ़ निर्माण की प्रक्रिया में, मुख्य समय लेने वाली गणनाओं को दो प्रकारों में विभाजित किया जा सकता है:

1. बहुपदों पर आधारित एनटीटी (संख्या सैद्धांतिक परिवर्तन) गणना

2. अण्डाकार वक्रों पर एमएसएम (मल्टी-स्केलर गुणन) गणना। सामान्यतया, ZK प्रूफ द्वारा उत्पन्न गणना में, NTT-प्रकार के कंप्यूटिंग कार्य सभी कंप्यूटिंग कार्यों का लगभग 25% और MSM-प्रकार के कंप्यूटिंग कार्य लगभग 60-70% के लिए जिम्मेदार होते हैं।

सौभाग्य से, ये दो प्रकार के कंप्यूटिंग कार्य मौजूद हैं:

1. तर्क अपेक्षाकृत सरल है

2. एक ही कंप्यूटिंग तर्क की बड़ी संख्या में पुनरावृत्ति

3. समानता की विशेषताएं (बिटकॉइन माइनिंग कंप्यूटिंग के समान)। इसलिए, इन दो प्रकार की गणनाओं में तेजी लाने के लिए उच्च-प्रदर्शन वाले हार्डवेयर का उपयोग करना सैद्धांतिक रूप से संभव है।

जैसा कि नीचे दिए गए चित्र में दिखाया गया है, हम पा सकते हैं कि एनटीटी गणना (ऊपरी बाएँ भाग) और एमएसएम गणना (दाईं ओर) ZK प्रूफ पीढ़ी के वर्कफ़्लो में हल्के ढंग से युग्मित हैं। इसलिए, ZK प्रोजेक्ट पार्टी वास्तविक जरूरतों के अनुसार चयन कर सकती है:

1. अकेले एनटीटी गणना में तेजी लाएं या

2. अकेले एमएसएम गणना में तेजी लाएं

3. एनटीटी और एमएसएम को समग्र रूप से तेज करें, तीन विकल्प।

सामान्य ZK प्रूफ जनरेशन प्रक्रिया का वर्कफ़्लो

- नोट 1: ऊपर दी गई तस्वीर स्क्रॉल के सह-संस्थापक झांग ये के पेपर से है: पाइपज़ेडके: पाइपलाइन आर्किटेक्चर के साथ शून्य-ज्ञान प्रमाण को तेज करना। यह zk हार्डवेयर एक्सेलेरेशन का अध्ययन करने वाले उद्योग के पहले पेपरों में से एक है।

- नोट 2: कुछ साहित्य/लेखों में, यह दावा किया गया है कि सबसे अधिक समय लेने वाली ZK प्रूफ पीढ़ी FFT (फास्ट फूरियर ट्रांसफॉर्म) और MSM है। यद्यपि एफएफटी और एनटीटी के सिद्धांत समान हैं, क्योंकि जेडके में शामिल अधिकांश क्रिप्टोग्राफ़िक गणना परिमित फ़ील्ड (परिमित फ़ील्ड) पर की जाती हैं, वास्तविक गणना एनटीटी होनी चाहिए। इसलिए, हम अधिकांश शैक्षणिक लेखों में प्रयुक्त एनटीटी को मानक के रूप में लेते हैं।

हार्डवेयर त्वरण का उपयोग किसमें किया जाता है?

खनन समाधान के समान, वर्तमान ZK हार्डवेयर त्वरण समाधान मुख्य रूप से निम्नलिखित तीन प्रकार के हार्डवेयर के माध्यम से कार्यान्वित किया जाता है:

- GPU

- FPGA

- ASICs

वर्तमान में, बाज़ार में दो मुख्य हार्डवेयर त्वरण समाधान उपलब्ध हैं: GPU और FPGA। GPU/FPGA का उपयोग करके त्वरण योजनाएं लागू करना अपेक्षाकृत आसान है। इसलिए, बाज़ार पर तेज़ी से कब्ज़ा करने के लिए, अधिकांश निर्माता पहले GPU/FPGA समाधान लागू करेंगे। GPU और FPGAs की उच्च हार्डवेयर लागत, अपेक्षाकृत उच्च बिजली की खपत और सीमित पूर्ण प्रदर्शन के कारण। इसलिए, ASIC समाधान एक ऐसा हिस्सा है जिसे ZK हार्डवेयर त्वरण पारिस्थितिकी तंत्र में नजरअंदाज नहीं किया जा सकता है।

हार्डवेयर एक्सेलेरेशन ZK प्रोजेक्ट पार्टी को कैसे सेवा प्रदान करता है

ZK हार्डवेयर त्वरण प्रदाता दो तरीकों से ZK-प्रूफ पीढ़ी त्वरण सेवाएँ प्रदान कर सकते हैं:

- SaaS API के माध्यम से।

- हार्डवेयर (संपूर्ण मशीन/चिप) बेचकर त्वरण सेवाएं (खनन मशीनें बेचने के समान) प्रदान करें।

जैसा कि हमने ऊपर उल्लेख किया है, ZK प्रमाणों की पीढ़ी के दौरान, NTT और MSM गणनाएँ हल्के ढंग से युग्मित होती हैं। इसलिए, विभिन्न सेवा ग्रैन्युलैरिटी के अनुसार, हार्डवेयर त्वरण सेवा प्रदाता निम्नलिखित तीन ग्रैन्युलर सेवाएं प्रदान कर सकते हैं।

- समर्पित एनटीटी एक्सेलेरेशन (समर्पित एनटीटी एक्सेलेरेशन एपीआई/हार्डवेयर डिवाइस)

- समर्पित एमएसएम त्वरण (समर्पित एमएसएम त्वरण एपीआई/हार्डवेयर डिवाइस)

- एक ही समय में एनटीटी और एमएसएम में तेजी लाने के लिए ऑल-इन-वन त्वरण समाधान।

हार्डवेयर एक्सेलेरेशन प्रदाताओं में अंतर

एनटीटी और एमएसएम कंप्यूटिंग समस्याओं का कई वर्षों से बड़े पैमाने पर अध्ययन किया गया है। प्रमुख निर्माताओं के लिए कम समय में कंप्यूटिंग सिद्धांत में सफलता हासिल करना मुश्किल है। इसलिए, विभिन्न निर्माताओं के बीच तकनीकी अंतर इंजीनियरिंग प्राप्ति क्षमताओं, एल्गोरिदम विवरण के नियंत्रण, प्रौद्योगिकी स्टैक (हार्डवेयर) चयन, हार्डवेयर उत्पादन की लागत नियंत्रण और उत्पाद डिजाइन क्षमताओं में अधिक निहित है। जब ग्राहक एक त्वरण विक्रेता चुनते हैं, तो वे निम्नलिखित तीन कारकों पर ध्यान केंद्रित करेंगे:

- एक ही कंप्यूटिंग कार्य के तहत हार्डवेयर/सेवा का प्रदर्शन और निर्माता का कंप्यूटिंग समय।

- हार्डवेयर त्वरण लागत, उसी कंप्यूटिंग कार्य के तहत, निर्माता की कंप्यूटिंग लागत है।

- एपीआई/डिवाइस के उपयोग में आसानी।

हम सिसिक में निवेश क्यों करते हैं?

सिसिक की स्थापना अगस्त 2022 के अंत में लियो फैन और बोवेन हुआंग द्वारा की गई थी। Cysic का मुख्य लक्ष्य ZK प्रोजेक्ट की ZK-प्रूफ़ पीढ़ी प्रक्रिया के लिए हार्डवेयर त्वरण सेवाएँ प्रदान करना है। कैलिफ़ोर्निया, संयुक्त राज्य अमेरिका और मुख्यभूमि चीन। इन संस्थापक सदस्यों की पृष्ठभूमि मुख्य रूप से संयुक्त राज्य अमेरिका के शीर्ष 20 विश्वविद्यालयों के कंप्यूटर विज्ञान विभाग से पीएचडी और कंप्यूटिंग प्रौद्योगिकी संस्थान, चीनी विज्ञान अकादमी की चिप डिजाइन टीम से है।

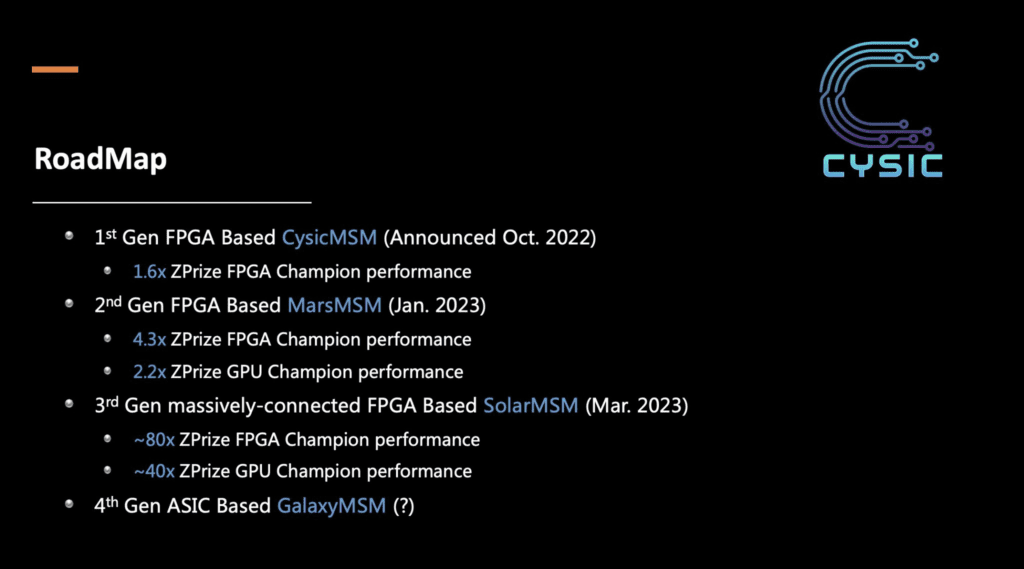

इस स्तर पर, परियोजना ने एफपीजीए-आधारित एमएसएम गणना के पीओसी सत्यापन का एहसास किया है, और परियोजना कोड सोलरएमएसएम है। इस स्तर पर, सोलरएमएसएम SaaS के माध्यम से बाहरी सेवाएं प्रदान करेगा।

वर्तमान में, Cysic कई प्रमुख ZK परियोजना दलों के साथ सहयोग के इरादे तक पहुँच गया है और निकट भविष्य में उन्हें परीक्षण सेवाएँ प्रदान करेगा। कई उद्योग अधिकारियों के साक्ष्य के अनुसार, एमएसएम कंप्यूटिंग प्रदर्शन में तेजी लाने में सोलरएमएसएम उद्योग में शीर्ष स्तर की स्थिति में है।

संस्थापक टीम प्रोफ़ाइल

दोनों संस्थापकों के पास मजबूत तकनीकी पृष्ठभूमि है और वे क्रिप्टोग्राफी और हार्डवेयर डिजाइन के विशेषज्ञ हैं। डॉ. लियो ने क्रिप्टोग्राफी के अंतरराष्ट्रीय स्तर पर प्रसिद्ध प्रोफेसर एलेन शी के संरक्षण में कॉर्नेल विश्वविद्यालय से स्नातक की उपाधि प्राप्त की। रटगर्स विश्वविद्यालय में सहायक प्रोफेसर के रूप में शामिल होने से पहले, लियो ने अल्गोरंड में एक क्रिप्टोग्राफी शोधकर्ता के रूप में काम किया।

एक अन्य संस्थापक, बोवेन हुआंग ने सिसिक की स्थापना करने और पीएचडी की पढ़ाई के लिए येल विश्वविद्यालय जाने से पहले 6 साल तक इंस्टीट्यूट ऑफ कंप्यूटिंग टेक्नोलॉजी, चाइनीज एकेडमी ऑफ साइंसेज में काम किया। डिजाइन लैंडिंग.

पीओसी परिणाम

वर्तमान में, Cysic ने Xilinx के सार्वजनिक FPGA, कोड-नाम सोलरMSM के आधार पर MSM त्वरण समाधान के POC डिज़ाइन को लागू किया है। पीओसी सत्यापन में, एमएसएम कंप्यूटिंग कार्य के लिए जिसका इनपुट आकार 2³⁰ है, सोलरएमएसएम इसे एक सेकंड से भी कम समय में तेज कर सकता है। यह वर्तमान में उद्योग में सभी सार्वजनिक डेटा परिणामों के बीच सबसे मजबूत स्तर है, और यह ZPrize प्रतियोगिता के चैंपियन प्रदर्शन से 1-2 ऑर्डर अधिक है।

सोलरएमएसएम का त्वरित कार्यान्वयन दर्शाता है:

- Cysic टीम के पास कुशल R&D ताकत और तकनीकी क्षमताएं हैं। इसे शीघ्रता से डिज़ाइन और कार्यान्वित किया जा सकता है, जो कि पहले ZPrize की तुलना में 1-2 ऑर्डर अधिक है, जो अत्यधिक गति लाभ दर्शाता है।

- सिसिक टीम के पास एक मजबूत आपूर्ति श्रृंखला एकीकरण प्रबंधन क्षमता है। यदि पीसीबी, गर्मी अपव्यय, बिजली की आपूर्ति, पीसीआईई कनेक्टर और चेसिस संरचना सभी को समानांतर में अनुकूलित किया जाता है, तो डिलीवरी अभी भी 2-3 महीनों के भीतर जल्दी से पूरी की जा सकती है, जो मूल रूप से उद्योग मानक की गति से 2-3 गुना अधिक है।

साथ ही, इस स्तर पर POC, Cysic हार्डवेयर डिज़ाइन/विकास कार्य का आंतरिक सत्यापन भी है। क्योंकि ASIC चिप्स की त्रुटि सुधार लागत FPGA समाधानों की तुलना में अधिक है, उच्च बैंडविड्थ, उच्च बिजली की खपत और उच्च इंटरकनेक्शन स्तरों पर सोलरएमएसएम के माध्यम से पूर्ण मशीन सत्यापन भविष्य में ASIC चिप त्रुटियों के जोखिम को काफी कम कर सकता है।

प्रौद्योगिकी रोडमैप

Cysic की योजना NTT और MSM कंप्यूटिंग सहित संपूर्ण ASIC हार्डवेयर एक्सेलेरेशन समाधान प्रदान करने की है। वर्तमान में, प्रोजेक्ट पार्टी दो-चरणीय R&D रणनीति अपनाती है।

चरण 1: एफपीजीए-आधारित पीओसी

परियोजना के पहले चरण में, एक्सिलिनक्स के सार्वजनिक एफपीजीए: सोलरएमएसएम पर आधारित एमएसएम और एनटीटी त्वरण का एक पीओसी संस्करण। वर्तमान में, एमएसएम कंप्यूटिंग त्वरण मॉड्यूल पूरा हो चुका है, और 2³⁰-स्केल एमएसएम कंप्यूटिंग को एक सेकंड से भी कम समय में पूरा किया जा सकता है, जो सभी सार्वजनिक एफपीजीए-एमएसएम हार्डवेयर त्वरण परिणामों के बीच उच्चतम प्रदर्शन है, जो प्रतिस्पर्धा में अग्रणी है। परिमाण के 1-2 क्रम। यदि और कुछ नहीं, तो ASIC चिप्स आने तक सोलरएमएसएम एमएसएम हार्डवेयर त्वरण के लिए उच्चतम प्रदर्शन रिकॉर्ड रखेगा। Cysic कई प्रमुख ZK परियोजनाओं के साथ सहयोग के इरादे तक पहुँच गया है और सबसे पहले इन परियोजनाओं के लिए MSM त्वरण सेवाएँ प्रदान करेगा।

अगले कुछ महीनों में, सिसिक ने सोलरएमएसएम पर आधारित एनटीटी कंप्यूटिंग एक्सेलेरेशन मॉड्यूल सोलरएनटीटी को पूरा करने की योजना बनाई है। समान बड़े पैमाने पर एफपीजीए इंटरकनेक्शन सिस्टम के आधार पर त्वरित कंप्यूटिंग करने के लिए सोलरएनटीटी और सोलरएमएसएम को एक ही सर्वर पर तैनात किया जाएगा। कार्यान्वयन के इन दो सेटों को ऑल-इन-वन एक्सेलेरेशन समाधान, सोलरज़ेडकेपी बनने के लिए सिसिक द्वारा डिजाइन किए गए हाई-स्पीड इंटरकनेक्शन आर्किटेक्चर के माध्यम से एकीकृत किया जाएगा। सोलरZKP SaaS के माध्यम से बाह्य रूप से API सेवाएँ प्रदान करेगा।

चरण 2: 12एनएम एएसआईसी

POC चरण के बाद, Cysic 12nm ASIC विकास चरण शुरू करेगा। लक्ष्य एकल ASIC चिप की कंप्यूटिंग शक्ति को पूरे सोलरZKP (एमएसएम और एनटीटी कंप्यूटिंग और प्रोजेक्ट पार्टी द्वारा निर्दिष्ट अन्य मुख्य कार्यों दोनों का समर्थन) के प्रदर्शन तक पहुंचना है, जबकि एकल चिप की बिजली खपत को दो ऑर्डर तक कम करना है। परिमाण।

बाजार का विश्लेषण

ग्राहक हार्डवेयर त्वरण समाधान कैसे चुनते हैं??

वास्तविक उत्पादन में, अलग-अलग ZK ग्राहकों की हार्डवेयर त्वरण के लिए अलग-अलग आवश्यकताएं होती हैं, यह इस बात पर निर्भर करता है कि ZK प्रोजेक्ट प्रूफ जेनरेशन समय के प्रति कितना संवेदनशील है। उदाहरण के लिए:

- ZkEVM/zkVM पर आधारित लेयर-2 परियोजनाओं के लिए, उनकी मुख्य आवश्यकता ZK प्रमाणों की तेज़ और स्थिर पीढ़ी है। इसलिए, वे तेज़ और अधिक स्थिर एकीकृत त्वरण समाधान चुनने के लिए अधिक इच्छुक होंगे।

- कुछ ZK परियोजनाओं के लिए जो ZK प्रूफ़ के निर्माण समय के प्रति संवेदनशील नहीं हैं, उन्हें सबसे तेज़ गति से प्रूफ़ उत्पन्न करने की आवश्यकता नहीं है, जैसे एक्सचेंजों के संपत्ति प्रमाण। इस परिदृश्य में, ग्राहक लचीले ढंग से अकेले एमएसएम कंप्यूटिंग त्वरण का चयन कर सकते हैं या सर्वोत्तम मूल्य चुनने के लिए स्वीकार्य समय के भीतर विभिन्न सेवा प्रदाताओं द्वारा प्रदान की गई एमएसएम कंप्यूटिंग और एनटीटी कंप्यूटिंग को जोड़ सकते हैं।

हमारा मानना है कि भविष्य में, ऐसे उपकरण होंगे जो ग्राहकों को इष्टतम समाधान उत्पन्न करने में मदद करने के लिए विभिन्न हार्डवेयर त्वरण विक्रेताओं के समाधानों को संयोजित करेंगे।

परियोजना जोखिम

वर्तमान में, कई कंपनियों ने ZK हार्डवेयर त्वरित ट्रैक पर प्रतियोगिता में भाग लिया है। ASIC-आधारित ZK हार्डवेयर त्वरण परियोजनाओं के लिए परियोजना विकास में देरी के जोखिम और बाजार जोखिम हैं।

परियोजना विकास में देरी का जोखिम

ZK प्रोजेक्ट पार्टी और ZK हार्डवेयर एक्सेलेरेशन निर्माता के बीच आपसी सहयोग और आपसी उपलब्धि का रिश्ता है। ZK प्रोजेक्ट पार्टी के रूप में, यह ZK प्रोजेक्ट की बाजार हिस्सेदारी को जब्त करने के लिए पहले उपलब्ध हार्डवेयर त्वरण समाधान का चयन करेगा। ZkEVM/zkVM प्रोजेक्ट के लिए, L2 ब्लॉक प्रूफ़ प्रदान करने में सक्षम होना सबसे महत्वपूर्ण विचारों में से एक है। इसलिए, कुछ ZK परियोजना पार्टियाँ प्रारंभिक चरण में हार्डवेयर त्वरण विक्रेताओं के साथ दीर्घकालिक सहयोग के इरादे तक पहुँचेंगी। यदि परियोजना का विकास बहुत धीमा है, तो शुरुआती चरण में बाजार हिस्सेदारी का कुछ हिस्सा खो सकता है। वहीं, ASIC टेप-आउट में विफलता का जोखिम भी है। चिप निर्माताओं की क्षमता बाधाओं से प्रभावित होकर, टेप-आउट विफलताएं परियोजना को टेप-आउट को फिर से शेड्यूल करने के लिए बाध्य करेंगी, जिससे परियोजना में देरी होगी।

बाजार ज़ोखिम

ZK प्रोजेक्ट पार्टी को दो श्रेणियों में विभाजित किया जा सकता है: गोपनीयता श्रेणी और विस्तार श्रेणी। गोपनीयता परियोजनाओं के लिए, हार्डवेयर त्वरण का उपयोग करने से साइड-चैनल हमलों का जोखिम कुछ हद तक कम हो सकता है, लेकिन गोपनीयता के मुद्दों पर विचार करते हुए, गोपनीयता परियोजनाएं ZK हार्डवेयर त्वरण समाधान चुनने में अधिक सतर्क होंगी, जैसे SaaS के माध्यम से नहीं के बजाय सीधे हार्डवेयर खरीदने का चयन करना सेवा।

प्रतिस्पर्धी परियोजना प्रमुख प्रतियोगिता

वर्तमान में, उद्योग में तीन शक्तिशाली प्रतिस्पर्धी हैं, जिनके नाम हैं सुप्रानैशनल, उलवंतन्ना और ऑराडाइन।

इस अंतर्राष्ट्रीय

सुपरनैशनल ने 2019 से GPU-त्वरित ZK ट्रैक में प्रवेश किया है और हाल ही में FPGA/ASIC क्षेत्र को शामिल करना शुरू किया है। सुपरनैशनल के पास पहले से ही एक बहुत ही परिपक्व ओपन-सोर्स जीपीयू-आधारित त्वरण समाधान है, और इसका प्रदर्शन उद्योग में सबसे आगे है। साथ ही, हम उम्मीद करते हैं कि सुपरनैशनल के पास बेहतर प्रदर्शन के साथ एक वाणिज्यिक क्लोज्ड-सोर्स समाधान भी हो। कुछ उद्योग संसाधनों और अच्छे नकदी प्रवाह के साथ, सुपरनैशनल ने पहले बाजार में प्रवेश किया।

उलवन्तन्ना

संस्थापक टीम जंप क्रिप्टो से है और उसने पैराडाइम और बेन क्रिप्टो से निवेश प्राप्त किया है। इसकी ताकत को कम नहीं आंका जाना चाहिए.

ऑराडाइन

सीनियर की तुलना में, संस्थापक टीम के पास समृद्ध उद्यमशीलता अनुभव और शीर्ष निर्माताओं और पूंजी का एक मंच है।

अन्य हार्डवेयर एक्सेलेरेशन टीमें

सार्वजनिक आंकड़ों के अनुसार, बाकी टीमें, जैसे इंगोन्यामा और जंप क्रिप्टो, ने उनसे पहले ट्रैक में प्रवेश किया, लेकिन इस स्तर पर उनका प्रदर्शन सोलरएमएसएम जितना अच्छा नहीं है।

ZK परियोजना आंतरिक हार्डवेयर त्वरण टीम

वर्तमान में, समर्पित हार्डवेयर त्वरण टीमों के अलावा, कई ZK प्रोजेक्ट पार्टियाँ आंतरिक रूप से zkSync और स्क्रॉल जैसे हार्डवेयर त्वरण समाधान भी तलाश रही हैं।

zkSync

zkSync GPU/FPGA त्वरण समाधान चुनता है। ZPrice पर प्रकाशित परिणामों के अनुसार, इनपुट स्केल 2.528²⁶ MSM होने पर zkSync का GPU समाधान 2 सेकंड लेता है। यह प्रदर्शन सिसिक सोलरएमएसएम समाधान के दसवें हिस्से से भी कम है (2³⁰ एमएसएम गणना में 1 सेकंड से भी कम समय लगता है)।

स्क्रॉल

स्क्रॉल GPU-आधारित त्वरण के लिए आंतरिक रूप से शोध किया गया है। साथ ही, स्क्रॉल और कुछ अकादमिक संस्थान बेहतर समाधान तलाशने के लिए सहयोग कर रहे हैं, और उनके नवीनतम अकादमिक शोध परिणाम एएसपीएलओएस 2023 में प्रकाशित हुए थे, जो कंप्यूटर आर्किटेक्चर के क्षेत्र में शीर्ष सम्मेलन है [3]। अग्रणी zkEVM परियोजना के रूप में, यह उनकी अनुवर्ती प्रगति की प्रतीक्षा करने और उस पर नज़र रखने के लायक है।

संदर्भ

[1] पाइपज़ेडके: पाइपलाइन आर्किटेक्चर के साथ शून्य-ज्ञान प्रमाण को तेज करना, झांगये [2] मल्टी-स्केलर गुणन का एफपीजीए त्वरण: साइक्लोनएमएसएम, जंपक्रिप्टो [3] जीजेडकेपी: एक जीपीयू त्वरित शून्य-ज्ञान प्रूफ सिस्टमअस्वीकरण: इस वेबसाइट पर जानकारी सामान्य बाजार टिप्पणी के रूप में प्रदान की जाती है और निवेश सलाह का गठन नहीं करती है। हम आपको निवेश करने से पहले अपना खुद का शोध करने के लिए प्रोत्साहित करते हैं।

खबरों पर नज़र रखने के लिए हमसे जुड़ें: https://linktr.ee/coincu

हेरोल्ड

सिक्का समाचार