ZK Proof スタートアップ Cysic が ZK ハードウェア アクセラレーション ロードマップをどのように突破したか

キーポイント:

- ゼロ知識ハードウェアのスタートアップである Cysic は、最近 Polychain Capital 主導の 6 万ドルのシード資金調達ラウンドを完了しました。

- Cysic の主な目標は、ZK プロジェクトの ZK プルーフ生成プロセスにハードウェア アクセラレーションによるサービスを提供することです。

- Cysic はすでにいくつかの主要な ZK プロジェクトと提携する意向に達しており、まずこれらのプロジェクトに MSM アクセラレーション サービスを提供します。

Cysic は、ZK 耐性の生成時間を短縮するための高度な ASIC チップの設計に特化した、業界をリードする ZK ハードウェア アクセラレーション プロジェクトです。 Cysic は一流のハードウェア設計および開発チームを結成し、FPGA ベースの POC 設計作業を完了しました。

POC の結果によれば、Cysic の ZK ハードウェア アクセラレーション機能はすでに業界をリードする地位にあることが証明されています。

ABCDEはシードラウンドでCysicに投資しており、今回の投資機関にはPolychain、A&T、Hashkey、Web3.com Ventureも含まれる。

ZK ハードウェア アクセラレーションが必要な理由は何ですか?

ZKプルーフの生成(ZKプルーフジェネレーション) これは、ZK プロジェクトの中核となるステップの 1 つです。残念ながら、既存の ZK 証明システムでは、ZK 証明の生成には通常、大量の計算が必要です。プロジェクトの複雑さが増し、ZK 回路の規模が増大するにつれて、ZK 証明の生成に必要な計算量は指数関数的に増加します。

たとえば、Scroll や zkSync などの大規模な zkEVM/zkVM プロジェクトの場合、CPU を使用して ZK プルーフを生成すると、計算に数時間、場合によっては数日かかる場合があります。実際のビジネスでは、ほとんどのプロジェクトで ZK プルーフの生成を数秒から数分に制限する必要があります。ほとんどの ZK プロジェクト、特に zkEVM/zkVM などの拡張プロジェクトでは、数時間以上の計算時間はまったく受け入れられません。

さらに、ZK 証明生成の計算の複雑さは、理論的には、ZK プロジェクトが将来正式に開始されるまでの約 2 年の時間枠内で軽減するのは困難です。

したがって、プロジェクトの使いやすさを確保するために、プロジェクトが正式に開始される前に、ZKプロジェクト当事者は、ZKプルーフの生成を秒レベルまたは分レベルまで加速する「ZKプルーフの生成を加速する」という技術的ソリューションを採用する必要があります。 。現在、高性能ハードウェアによって ZK 耐性の生成を高速化する方法が第一の選択肢となっています。

ハードウェアアクセラレーションとは何ですか?

ZK プルーフの生成プロセスでは、時間のかかる主な計算は 2 つのタイプに分類できます。

1. 多項式に基づく NTT (Number Theoretic Transform) 計算

2. 楕円曲線上の MSM (マルチスカラー乗算) 計算。一般に、ZK 証明によって生成される計算では、NTT タイプの計算タスクが全計算タスクの約 25% を占め、MSM タイプの計算タスクが約 60 ~ 70% を占めます。

幸いなことに、次の 2 種類のコンピューティング タスクが存在します。

1. ロジックは比較的単純です

2. 同じ計算ロジックの多数の繰り返し

3. 並列処理の特性 (ビットコイン マイニング コンピューティングと同様)。したがって、高性能ハードウェアを使用してこれら XNUMX 種類の計算を高速化することは理論的には可能です。

以下の図に示すように、ZK プルーフ生成のワークフローでは、NTT 計算 (左上部分) と MSM 計算 (右側) が軽く結合されていることがわかります。したがって、ZK プロジェクト関係者は実際のニーズに応じて選択できます。

1. NTT計算を単独で高速化するか、

2.MSM計算のみを高速化する

3. NTTとMSM全体で加速する、XNUMXつの選択肢。

一般的な ZK プルーフ生成プロセスのワークフロー

- 注 1: 上の画像は、Scroll の共同創設者である Zhang Ye の論文「PipeZK: Accelerated Zero-Knowledge Proof with a Pipelined Architecture」からのものです。これは、zk ハードウェア アクセラレーションを研究した業界初の論文の XNUMX つです。

- 注 2: 一部の文献/記事では、ZK 証明の生成に最も時間がかかるのは FFT (高速フーリエ変換) と MSM であると主張されています。 FFT と NTT の原理は似ていますが、ZK に含まれる暗号計算のほとんどは有限体 (Finite Field) 上で実行されるため、実際の計算は NTT が行う必要があります。したがって、ほとんどの学術論文で使用されている NTT を標準とします。

ハードウェア アクセラレーションとは何ですか?

マイニング ソリューションと同様に、現在の ZK ハードウェア アクセラレーション ソリューションは主に次の 3 種類のハードウェアを通じて実装されています。

- GPU

- FPGA

- ASIC

現在、市場では GPU と FPGA という 2 つの主要なハードウェア アクセラレーション ソリューションが利用可能です。 GPU/FPGA を使用したアクセラレーション スキームは比較的簡単に実装できます。したがって、市場をより早く掌握するために、ほとんどのメーカーはまず GPU/FPGA ソリューションを実装します。 GPU と FPGA のハードウェア コストが高く、消費電力が比較的高く、絶対的なパフォーマンスが限られているためです。したがって、ASIC ソリューションは、ZK ハードウェア アクセラレーション エコシステムにおいて無視できない部分です。

ハードウェア アクセラレーションが ZK プロジェクト パーティにどのように役立つか

ZK ハードウェア アクセラレーション プロバイダーは、次の 2 つの方法で ZK プルーフ生成アクセラレーション サービスを提供できます。

- SaaS API 経由。

- ハードウェア(マシン/チップ全体)を販売することにより、アクセラレーション サービス(マイニング マシンの販売と同様)を提供します。

上で述べたように、ZK 証明の生成中、NTT と MSM の計算は軽く結合されます。したがって、ハードウェア アクセラレーション サービス プロバイダーは、さまざまなサービス粒度に応じて、次の 3 つの粒度のサービスを提供できます。

- 専用 NTT アクセラレーション (専用 NTT アクセラレーション API/ハードウェア デバイス)

- 専用MSMアクセラレーション(専用MSMアクセラレーションAPI/ハードウェアデバイス)

- NTT と MSM を同時に高速化するオールインワンの高速化ソリューション。

ハードウェア アクセラレーション プロバイダーの違い

NTT と MSM のコンピューティングの問題は、長年にわたって広範囲に研究されてきました。大手メーカーが短期間にコンピューティング理論のブレークスルーを達成することは困難です。したがって、さまざまなメーカー間の技術的な違いは、エンジニアリング実現能力、アルゴリズム詳細の制御、技術スタック (ハードウェア) の選択、ハードウェア生産のコスト管理、および製品設計能力にあります。顧客がアクセラレーション ベンダーを選択するときは、次の 3 つの要素に重点を置きます。

- 同じコンピューティング タスクにおけるメーカーのハードウェア/サービスのパフォーマンスとコンピューティング時間。

- 同じコンピューティング タスクにおけるハードウェア アクセラレーション コストは、メーカーのコンピューティング コストとなります。

- API/デバイスの使いやすさ。

Cysic に投資する理由

Cysic は、Leo Fan 氏と Bowen Huang 氏によって 2022 年 20 月下旬に設立されました。 Cysic の主な目標は、ZK プロジェクトの ZK-proof 生成プロセスにハードウェア アクセラレーション サービスを提供することです。カリフォルニア、米国、そして中国本土。これらの創設メンバーの経歴は、主に米国のトップ XNUMX 大学のコンピュータ サイエンス学科の博士号取得者および中国科学院計算技術研究所のチップ設計チームからの出身です。

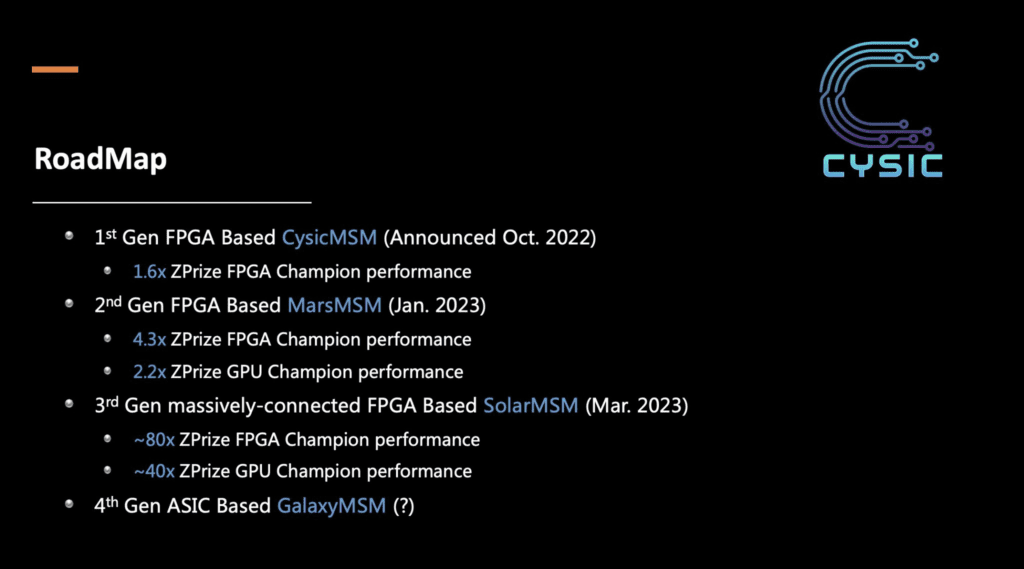

現段階では、プロジェクトはFPGAベースのMSM計算のPOC検証を実現しており、プロジェクトコードはSolarMSMです。現段階では、SolarMSM は SaaS を通じて外部サービスを提供します。

現在、Cysic はいくつかの主要な ZK プロジェクト関係者と協力する意向に達しており、近い将来テスト サービスを提供する予定です。多くの業界当局の証拠によると、SolarMSM は MSM コンピューティング パフォーマンスの高速化において業界トップクラスの地位にあります。

創設チームのプロフィール

2 人の創設者は強力な技術的背景を持ち、暗号化とハードウェア設計の専門家です。レオ博士は、国際的に有名な暗号学の教授、エレイン・シーの指導の下、コーネル大学を卒業しました。ラトガース大学に助教授として入社する前は、レオはアルゴランドで暗号研究者として働いていました。

もう一人の創設者であるボーエン・ファンは、Cysic を設立し、博士号取得のためにイェール大学に進学する前に、中国科学院コンピューティング技術研究所で 6 年間勤務していました。デザイン着陸。

POCの結果

現在、Cysic は、ザイリンクスのパブリック FPGA (コード名 SolarMSM) に基づく MSM アクセラレーション ソリューションの POC デザインを実装しています。 POC 検証では、入力サイズが 2⁰ の MSM コンピューティング タスクの場合、SolarMSM はそれを 1 秒未満に加速できます。これは現在、業界のすべての公開データ結果の中で最も強力なレベルであり、ZPrize コンテストのチャンピオンのパフォーマンスよりも 2 ~ XNUMX 桁高いです。

SolarMSM の迅速な実装により、次のことが実証されます。

- Cysic チームは効率的な研究開発力と技術力を備えています。最初の ZPrize よりも 1 ~ 2 桁速く設計および実装でき、圧倒的なスピードの利点を示します。

- Cysic チームは、堅牢なサプライ チェーン統合管理機能を備えています。 PCB、放熱、電源、PCIE コネクタ、およびシャーシ構造をすべて並行してカスタマイズした場合でも、納品は 2 ~ 3 か月以内に迅速に完了できます。これは基本的に業界標準の 2 ~ 3 倍の速度です。

同時に、この段階の POC は、Cysic ハードウェア設計/開発作業の内部検証でもあります。 ASIC チップのエラー訂正コストは FPGA ソリューションのコストよりも高いため、高帯域幅、高消費電力、高相互接続レベルでの SolarMSM によるフルマシン検証により、将来の ASIC チップエラーのリスクを大幅に軽減できます。

技術ロードマップ

Cysic は、NTT および MSM コンピューティングを含む、完全な ASIC ハードウェア アクセラレーション ソリューションを提供する予定です。現在、プロジェクト当事者は二段階の研究開発戦略を採用しています。

フェーズ 1: FPGA ベースの POC

プロジェクトの第 2 フェーズでは、ザイリンクスのパブリック FPGA: SolarMSM に基づく MSM および NTT アクセラレーションの POC バージョンが使用されます。現在、MSM コンピューティング アクセラレーション モジュールが完成しており、1⁰ スケールの MSM コンピューティングは 2 秒未満で完了できます。これは、公開されているすべての FPGA-MSM ハードウェア アクセラレーション結果の中で最高のパフォーマンスであり、競合他社を XNUMX つ以上リードしています。 XNUMX ~ XNUMX 桁。少なくとも、SolarMSM は、ASIC チップが登場するまで、MSM ハードウェア アクセラレーションの最高のパフォーマンス記録を保持するでしょう。 Cysic は、いくつかの主要な ZK プロジェクトと協力する意向に達しており、まずこれらのプロジェクトに MSM アクセラレーション サービスを提供します。

Cysic は今後数か月以内に、SolarMSM をベースにした NTT コンピューティング アクセラレーション モジュール SolarNTT を完成させる予定です。 SolarNTT と SolarMSM は同じサーバー上に導入され、同じ大規模 FPGA 相互接続システムに基づいてアクセラレーション コンピューティングを実行します。これら 2 つの実装セットは、Cysic が設計した高速相互接続アーキテクチャを通じて統合され、オールインワンの加速ソリューション、SolarZKP になります。 SolarZKPはSaaSを通じてAPIサービスを外部に提供します。

フェーズ 2: 12nm ASIC

POC 段階の後、Cysic は 12nm ASIC 開発段階を開始します。目標は、単一チップの消費電力を XNUMX 桁に削減しながら、SolarZKP 全体 (MSM と NTT コンピューティングの両方、およびプロジェクト当事者が指定したその他のコア機能をサポート) のパフォーマンスに達する単一 ASIC チップの計算能力を達成することです。大きさ。

市場分析

顧客はハードウェア アクセラレーション ソリューションをどのように選択するか?

実際の運用では、ZK プロジェクトがプルーフ生成時間に対してどの程度敏感であるかに応じて、ZK の顧客ごとにハードウェア アクセラレーションに対する要件が異なります。例えば:

- zkEVM/zkVM に基づくレイヤー 2 プロジェクトの場合、その中心的な要件は ZK プルーフの高速かつ安定した生成です。したがって、より高速で安定した統合アクセラレーション ソリューションを選択する傾向が強まります。

- ZK プルーフの生成時間に敏感でない一部の ZK プロジェクトの場合、交換のプロパティ プルーフなど、最速でプルーフを生成する必要はありません。このシナリオでは、顧客は MSM コンピューティング アクセラレーションを単独で柔軟に選択することも、許容可能な時間内でさまざまなサービス プロバイダーが提供する MSM コンピューティングと NTT コンピューティングを組み合わせて最適な価格を選択することもできます。

将来的には、さまざまなハードウェア アクセラレーション ベンダーのソリューションを組み合わせて、お客様が最適なソリューションを生成できるツールが登場すると信じています。

プロジェクトのリスク

現在、多くの企業が ZK ハードウェア アクセラレーション トラックの競争に参加しています。 ASIC ベースの ZK ハードウェア アクセラレーション プロジェクトには、プロジェクト開発遅延のリスクと市場リスクが存在します。

プロジェクト開発遅延リスク

ZKプロジェクト当事者とZKハードウェアアクセラレーションメーカーの間には相互協力と相互成果の関係があります。 ZK プロジェクトの当事者として、ZK プロジェクト自体の市場シェアを獲得するために、最初に利用可能なハードウェア アクセラレーション ソリューションを選択します。 zkEVM/zkVM プロジェクトにとって、L2 ブロック証明を安定して提供できることは最も重要な考慮事項の XNUMX つです。したがって、一部の ZK プロジェクト関係者は、初期段階でハードウェア アクセラレーション ベンダーと長期的な協力関係に到達する予定です。プロジェクトの開発が遅すぎると、初期段階で市場シェアの一部が失われる可能性があります。同時に、ASIC テープアウトで障害が発生するリスクもあります。チップ メーカーの生産能力の制約の影響を受け、テープアウトが失敗すると、プロジェクトはテープアウトのスケジュールを変更しなければならなくなり、プロジェクトの遅延が発生します。

市場リスク

ZKプロジェクトパーティーはプライバシー部門と拡張部門の2つに分類できます。プライバシー プロジェクトの場合、ハードウェア アクセラレーションを使用すると、サイドチャネル攻撃のリスクがある程度軽減される可能性がありますが、プライバシーの問題を考慮すると、プライバシー プロジェクトは、SaaS 経由ではなくハードウェアを直接購入することを選択するなど、ZK ハードウェア アクセラレーション ソリューションを選択する際により慎重になります。サービス。

プロジェクトヘッドコンペティションに参加

現在、業界には Supranational、Ulvantanna、Auradine という 3 つの強力な競合他社が存在します。

超国家的

Supranational は 2019 年から GPU アクセラレーション ZK トラックに参入し、最近では FPGA/ASIC 分野にも関与し始めました。 Supranational は、非常に成熟したオープンソースの GPU ベースのアクセラレーション ソリューションをすでに持っており、そのパフォーマンスは業界の最前線にあります。同時に、Supranational がより優れたパフォーマンスを備えた商用のクローズドソース ソリューションも提供できることを期待しています。超国家企業は、一定の業界リソースと良好なキャッシュフローを備えて、より早く市場に参入しました。

ウルバンタナ

創設チームは Jump Crypto の出身で、paradigm と bain crypto から投資を受けています。その強さを過小評価すべきではありません。

オーラディン

シニアと比較して、創業チームは豊富な起業家経験とトップメーカーと資本のプラットフォームを持っています。

他のハードウェア アクセラレーション チーム

インゴンヤマやジャンプクリプトなどの残りのチームは彼らより先にコースに入ったが、公開データによると、彼らのパフォーマンスは現段階でソーラーMSMほど良くはありません。

ZK プロジェクト社内ハードウェア アクセラレーション チーム

現在、専任のハードウェア アクセラレーション チームに加えて、多くの ZK プロジェクト関係者が zkSync や Scroll などのハードウェア アクセラレーション ソリューションを社内で検討しています。

zkSync

zkSync は GPU/FPGA アクセラレーション ソリューションを選択します。 ZPrice で公開された結果によると、入力スケールが 2.528²⁶ MSM の場合、zkSync の GPU ソリューションは 2 秒かかります。このパフォーマンスは、Cysic SolarMSM ソリューションの 2 分の 1 未満です (XNUMX⁰ MSM の計算にかかる時間は XNUMX 秒未満です)。

スクロール

スクロール GPU ベースのアクセラレーションについて内部で研究されています。同時に、Scroll といくつかの学術機関はより良いソリューションを模索するために協力しており、最新の学術研究結果はコンピューター アーキテクチャ分野のトップカンファレンスである ASPLOS 2023 で発表されました [3]。主要な zkEVM プロジェクトとして、今後の進捗状況を楽しみにして追跡する価値があります。

参考文献

[1] PipeZK: パイプライン アーキテクチャによるゼロ知識証明の加速、ZhangYe [2] マルチスカラー乗算のFPGAアクセラレーション:CycloneMSM、JumpCrypto [3] GZKP: GPU で高速化されたゼロ知識証明システム免責事項: このウェブサイトの情報は一般的な市場解説として提供されており、投資アドバイスを構成するものではありません。 投資する前に、ご自身で調査を行うことをお勧めします。

ニュースを追跡するために私たちに参加してください: https://linktr.ee/coincu

ハロルド

コインク ニュース