Como o ZK Proof Startup Cysic avançou no roteiro de aceleração de hardware ZK

Pontos chave:

- Cysic, uma startup de hardware de conhecimento zero, concluiu recentemente uma rodada de financiamento inicial de US$ 6 milhões liderada pela Polychain Capital.

- O objetivo principal da Cysic é fornecer serviços acelerados por hardware para o processo de geração de provas ZK do projeto ZK.

- A Cysic já atingiu sua intenção de fazer parceria com alguns dos principais projetos ZK e primeiro fornecerá serviços de aceleração de HSH para esses projetos.

Cysic é um projeto de aceleração de hardware ZK líder do setor, dedicado a projetar chips ASIC avançados para ajudar a reduzir o tempo de geração à prova de ZK. Cysic formou uma equipe de design e desenvolvimento de hardware de primeira classe e concluiu o trabalho de design POC baseado em FPGA.

De acordo com os resultados do POC, pode-se provar que a capacidade de aceleração de hardware ZK da Cysic já está em uma posição de liderança no setor.

A ABCDE investiu na Cysic na rodada de sementes, e as instituições de investimento nesta rodada também incluem Polychain, A&T, Hashkey e Web3.com Venture.

Por que precisamos de aceleração de hardware ZK?

A geração da prova ZK (Geração de Prova ZK) é uma das etapas principais do projeto ZK. Infelizmente, nos sistemas de prova ZK existentes, a geração de provas ZK geralmente requer muitos cálculos. À medida que a complexidade do projeto aumenta e a escala do circuito ZK aumenta, a quantidade de cálculo necessária para a geração da prova ZK aumentará exponencialmente.

Por exemplo, para projetos zkEVM/zkVM de grande escala, como Scroll e zkSync, pode levar horas ou até dias de cálculo se usar a CPU para gerar provas ZK. Nos negócios reais, a maioria dos projetos precisa limitar a geração de provas ZK a segundos e minutos. O tempo de computação de várias horas ou mais é completamente inaceitável para a maioria dos projetos ZK, especialmente para projetos de expansão como zkEVM/zkVM.

Além disso, a complexidade computacional da geração de provas ZK é difícil de reduzir teoricamente no intervalo de tempo de cerca de dois anos antes do lançamento oficial do projeto ZK no futuro.

Portanto, para garantir a usabilidade do projeto, antes do lançamento oficial do projeto, a parte do projeto ZK deve adotar a solução técnica de “acelerar a geração de provas ZK” para acelerar a geração de provas ZK para o segundo ou minuto nível . O método de acelerar a geração à prova de ZK por meio de hardware de alto desempenho é atualmente a primeira escolha.

O que é acelerado por hardware?

No processo de geração de provas ZK, os principais cálculos demorados podem ser divididos em dois tipos:

1. Cálculo NTT (Number Theoretic Transform) baseado em polinômios

2. Cálculos MSM (multiplicação multiescalar) em curvas elípticas. De um modo geral, num cálculo gerado por uma prova ZK, as tarefas de computação do tipo NTT representam cerca de 25% de todas as tarefas de computação e as tarefas de computação do tipo MSM representam cerca de 60-70%.

Felizmente, existem estes dois tipos de tarefas de computação:

1. A lógica é relativamente simples

2. Um grande número de repetições da mesma lógica computacional

3. As características do paralelismo (semelhante à computação Bitcoin Mining). Portanto, é teoricamente viável utilizar hardware de alto desempenho para acelerar esses dois tipos de cálculos.

Conforme mostrado na figura abaixo, podemos descobrir que o cálculo NTT (parte superior esquerda) e o cálculo MSM (lado direito) são levemente acoplados no fluxo de trabalho de geração de prova ZK. Portanto, a parte do projeto ZK pode escolher de acordo com as necessidades reais:

1. Acelere o cálculo do NTT sozinho ou

2. Acelere o cálculo do MSM sozinho

3. Acelerar a NTT e os HSH como um todo, três opções.

Fluxo de trabalho do processo de geração de prova geral ZK

- Nota 1: A imagem acima é do artigo do cofundador da Scroll, Zhang Ye: PipeZK: Acelerando a prova de conhecimento zero com uma arquitetura em pipeline. Este é um dos primeiros artigos da indústria a estudar a aceleração de hardware zk.

- Nota 2: Em algumas literaturas/artigos, afirma-se que a geração de prova ZK mais demorada é FFT (Fast Fourier Transform) e MSM. Embora os princípios da FFT e do NTT sejam semelhantes, uma vez que a maioria dos cálculos criptográficos envolvidos no ZK são realizados em campos finitos (Campo Finito), o cálculo real deve ser o NTT. Portanto, tomamos como padrão o NTT utilizado na maioria dos artigos acadêmicos.

O que é a aceleração de hardware usada?

Semelhante à solução de mineração, a atual solução de aceleração de hardware ZK é implementada principalmente através dos três tipos de hardware a seguir:

- GPU

- FPGA

- ASICs

Atualmente, existem duas principais soluções de aceleração de hardware disponíveis no mercado: GPU e FPGA. Esquemas de aceleração usando GPU/FPGA são relativamente fáceis de implementar. Portanto, para conquistar o mercado mais rapidamente, a maioria dos fabricantes implementará primeiro a solução GPU/FPGA. Devido ao alto custo de hardware de GPUs e FPGAs, consumo de energia relativamente alto e desempenho absoluto limitado. Portanto, a solução ASIC é uma parte que não pode ser ignorada no ecossistema de aceleração de hardware ZK.

Como a aceleração de hardware atende ao grupo do projeto ZK

Os provedores de aceleração de hardware ZK podem fornecer serviços de aceleração de geração à prova de ZK de duas maneiras:

- Através de APIs SaaS.

- Fornecer serviços de aceleração (semelhantes à venda de máquinas de mineração) vendendo hardware (máquina inteira/chip).

Como mencionamos acima, durante a geração de provas ZK, os cálculos NTT e MSM são levemente acoplados. Portanto, de acordo com diferentes granularidades de serviço, os provedores de serviços de aceleração de hardware podem fornecer os três serviços granulares a seguir.

- Aceleração NTT Dedicada (API de Aceleração NTT Dedicada/Dispositivo de Hardware)

- Aceleração MSM dedicada (API/dispositivo de hardware dedicado de aceleração MSM)

- Solução de aceleração completa para acelerar NTT e MSM ao mesmo tempo.

Diferenças nos provedores de aceleração de hardware

Os problemas de computação NTT e MSM têm sido estudados extensivamente há muitos anos. É difícil para os grandes fabricantes alcançar avanços na teoria da computação em um curto período de tempo. Portanto, as diferenças técnicas entre os vários fabricantes residem mais nas capacidades de realização de engenharia, controle de detalhes de algoritmos, seleção de pilha de tecnologia (hardware), controle de custos de produção de hardware e capacidades de design de produto. Quando os clientes escolhem um fornecedor de aceleração, eles se concentram nos três fatores a seguir:

- O desempenho do hardware/serviço e o tempo de computação do fabricante sob a mesma tarefa de computação.

- O custo de aceleração de hardware, na mesma tarefa computacional, é o custo computacional do fabricante.

- Facilidade de uso da API/dispositivo.

Por que investimos na Cysic?

A Cysic foi fundada no final de agosto de 2022 por Leo Fan e Bowen Huang. O principal objetivo do Cysic é fornecer serviços de aceleração de hardware para o processo de geração à prova de ZK do projeto ZK. Califórnia, EUA e China continental. A formação desses membros fundadores vem principalmente dos doutorados do Departamento de Ciência da Computação das 20 melhores universidades dos Estados Unidos e da equipe de design de chips do Instituto de Tecnologia da Computação da Academia Chinesa de Ciências.

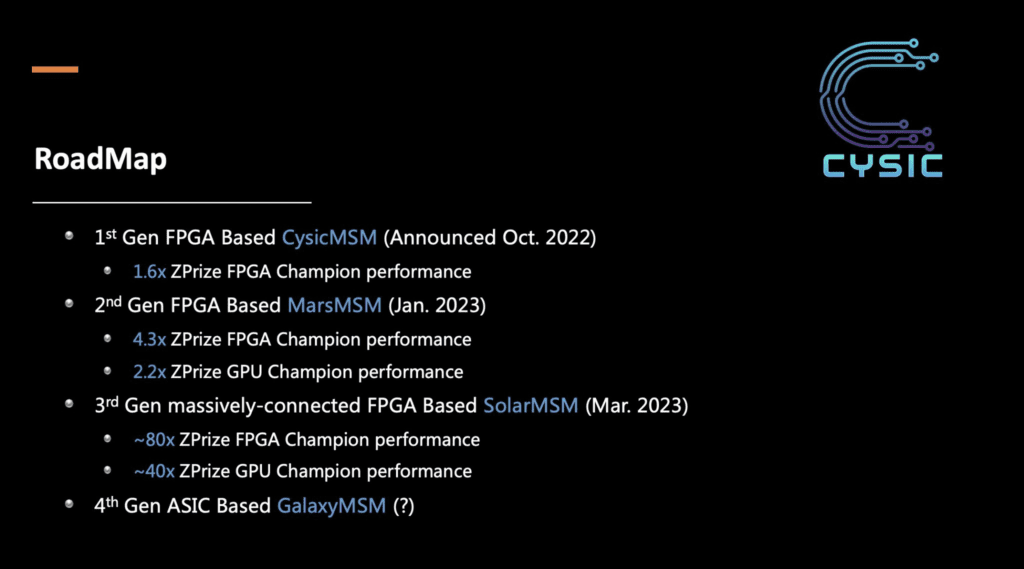

Nesta fase, o projeto realizou a verificação POC do cálculo MSM baseado em FPGA, e o código do projeto é SolarMSM. Nesta fase, a SolarMSM fornecerá serviços externos através de SaaS.

Atualmente, a Cysic alcançou intenções de cooperação com várias partes líderes do projeto ZK e irá fornecer-lhes serviços de teste num futuro próximo. De acordo com as evidências de muitas autoridades do setor, o SolarMSM está na posição de primeira linha do setor na aceleração do desempenho da computação MSM.

Perfil da equipe fundadora

Os dois fundadores têm sólida formação técnica e são especialistas em criptografia e design de hardware. Dr. Leo se formou na Universidade Cornell sob a tutela de uma professora de criptografia de renome internacional, Elaine Shi. Antes de ingressar na Rutgers University como professor assistente, Leo trabalhou como pesquisador de criptografia na Algorand.

Outro fundador, Bowen Huang, trabalhou no Instituto de Tecnologia da Computação da Academia Chinesa de Ciências por 6 anos antes de fundar a Cysic e ir para a Universidade de Yale para estudar para um doutorado. Aterrissagem de projeto.

Resultados POC

Atualmente, a Cysic implementou o design POC da solução de aceleração MSM baseada no FPGA público da Xilinx, codinome SolarMSM. Na verificação POC, para a tarefa de computação MSM cujo tamanho de entrada é 2³⁰, o SolarMSM pode acelerá-la para menos de um segundo. Atualmente, este é o nível mais forte entre todos os resultados de dados públicos do setor e é 1–2 ordens de magnitude superior ao desempenho do campeão da competição ZPrize.

A rápida implementação do SolarMSM demonstra:

- A equipe Cysic possui força eficiente de P&D e capacidades técnicas. Ele pode ser projetado e implementado rapidamente, o que é 1–2 ordens de magnitude maior que o primeiro ZPrize, mostrando uma vantagem esmagadora de velocidade.

- A equipe Cysic possui uma capacidade robusta de gerenciamento de integração da cadeia de suprimentos. Se o PCB, a dissipação de calor, a fonte de alimentação, os conectores PCIE e a estrutura do chassi forem todos personalizados em paralelo, a entrega ainda poderá ser concluída rapidamente em 2 a 3 meses, o que é basicamente 2 a 3 vezes a velocidade do padrão da indústria.

Ao mesmo tempo, o POC nesta fase também é uma verificação interna do trabalho de design/desenvolvimento de hardware Cysic. Como o custo de correção de erros dos chips ASIC é maior do que o das soluções FPGA, a verificação completa da máquina através do SolarMSM em alta largura de banda, alto consumo de energia e altos níveis de interconexão pode reduzir significativamente o risco de futuros erros no chip ASIC.

Roteiro Tecnológico

A Cysic planeja fornecer uma solução completa de aceleração de hardware ASIC, incluindo computação NTT e MSM. Atualmente, a parte do projeto adota uma estratégia de P&D em duas etapas.

Fase 1: POC baseado em FPGA

Na primeira fase do projeto, uma versão POC de aceleração MSM e NTT baseada no FPGA público da Xilinx: SolarMSM. Atualmente, o módulo de aceleração de computação MSM foi concluído e a computação MSM em escala de 2³⁰ pode ser concluída em menos de um segundo, que é o desempenho mais alto entre todos os resultados públicos de aceleração de hardware FPGA-MSM, liderando a competição por mais de 1–2 ordens de magnitude. No mínimo, o SolarMSM manterá o recorde de desempenho mais alto para aceleração de hardware MSM até que os chips ASIC sejam lançados. A Cysic alcançou intenções de cooperação com vários projetos líderes de ZK e primeiro fornecerá serviços de aceleração de HSH para esses projetos.

Nos próximos meses, Cysic planeja concluir o módulo de aceleração computacional NTT SolarNTT baseado em SolarMSM. SolarNTT e SolarMSM serão implantados no mesmo servidor para realizar computação acelerada com base no mesmo sistema de interconexão FPGA em larga escala. Esses dois conjuntos de implementações serão integrados por meio da arquitetura de interconexão de alta velocidade projetada pela Cysic para se tornar uma solução de aceleração completa, SolarZKP. SolarZKP fornecerá serviços de API externamente por meio de SaaS.

Fase 2: ASICs de 12 nm

Após a fase POC, a Cysic iniciará a fase de desenvolvimento ASIC de 12nm. O objetivo é atingir o poder de computação de um único chip ASIC, alcançando o desempenho de todo o SolarZKP (suportando computação MSM e NTT e outras funções básicas especificadas pela parte do projeto), reduzindo ao mesmo tempo o consumo de energia de um único chip para duas ordens de magnitude.

análise de mercado

Como os clientes escolhem soluções de aceleração de hardware?

Na produção real, diferentes clientes do ZK têm requisitos diferentes para aceleração de hardware, dependendo da sensibilidade do projeto ZK ao tempo de geração da prova. Por exemplo:

- Para projetos de Camada 2 baseados em zkEVM/zkVM, seu principal requisito é a geração rápida e estável de provas ZK. Portanto, eles estarão mais inclinados a escolher uma solução de aceleração integrada mais rápida e estável.

- Para alguns projetos ZK que não são sensíveis ao tempo de geração das provas ZK, eles não precisam gerar Provas na velocidade mais rápida, como as provas de propriedades de trocas. Nesse cenário, os clientes podem escolher com flexibilidade apenas a aceleração da computação MSM ou combinar a computação MSM e a computação NTT fornecidas por diferentes provedores de serviços dentro de um prazo aceitável para escolher o melhor preço.

Acreditamos que no futuro existirão ferramentas que combinarão soluções de diferentes fornecedores de aceleração de hardware para ajudar os clientes a gerar soluções ideais.

Risco do projeto

Atualmente, muitas empresas participaram da competição na pista acelerada de hardware ZK. Existem riscos de atraso no desenvolvimento de projetos e riscos de mercado para projetos de aceleração de hardware ZK baseados em ASIC.

Risco de atraso no desenvolvimento do projeto

Existe uma relação de cooperação mútua e realização mútua entre a parte do projeto ZK e o fabricante de aceleração de hardware ZK. Como parte do projeto ZK, ela escolherá primeiro a primeira solução de aceleração de hardware disponível para conquistar a participação de mercado do próprio projeto ZK. Para o projeto zkEVM/zkVM, ser capaz de fornecer provas de bloco L2 de forma estável é uma das considerações mais importantes. Portanto, algumas partes do projeto ZK alcançarão intenções de cooperação de longo prazo com fornecedores de aceleração de hardware na fase inicial. Se o desenvolvimento do projecto for demasiado lento, parte da quota de mercado poderá ser perdida numa fase inicial. Ao mesmo tempo, existe o risco de falha na saída da fita ASIC. Afetadas pelas restrições de capacidade dos fabricantes de chips, as falhas na fita forçarão o projeto a reprogramar a fita, causando atrasos no projeto.

Risco de mercado

A parte do projeto ZK pode ser dividida em duas categorias: a categoria de privacidade e a categoria de expansão. Para projetos de privacidade, o uso de aceleração de hardware pode reduzir até certo ponto o risco de ataques de canal lateral, mas considerando as questões de privacidade, os projetos de privacidade serão mais cautelosos na escolha de soluções de aceleração de hardware ZK, como optar por comprar hardware diretamente em vez de Não via SaaS serviço.

Competindo na competição principal do projeto

Actualmente, existem três concorrentes poderosos na indústria, nomeadamente Supranational, Ulvantanna e Auradine.

Supra nacional

A Supranational entrou no caminho ZK acelerado por GPU desde 2019 e recentemente começou a envolver o campo FPGA/ASIC. A Supranational já possui uma solução de aceleração baseada em GPU de código aberto muito madura e seu desempenho está na vanguarda da indústria. Ao mesmo tempo, esperamos que a Supranational também tenha uma solução comercial de código fechado e com melhor desempenho. A Supranational entrou no mercado mais cedo, com certos recursos do setor e bom fluxo de caixa.

Ulvantanna

A equipe fundadora é da Jump Crypto e recebeu investimentos da paradigma e da bain crypto. A sua força não deve ser subestimada.

Auradina

Em comparação com a Senior, a equipe fundadora possui uma rica experiência empreendedora e uma plataforma dos principais fabricantes e capital.

Outras equipes de aceleração de hardware

As demais equipes, como Ingonyama e Jump Crypto, entraram na pista antes delas, mas seu desempenho não é tão bom quanto o da SolarMSM nesta fase, segundo dados públicos.

Equipe interna de aceleração de hardware do projeto ZK

Atualmente, além de equipes dedicadas de aceleração de hardware, muitas partes do projeto ZK também estão explorando soluções de aceleração de hardware internamente, como zkSync e Scroll.

zkSyncName

zkSync escolhe solução de aceleração GPU/FPGA. De acordo com os resultados publicados no ZPrice, a solução GPU do zkSync leva 2.528 segundos quando a escala de entrada é 2²⁶ MSM. Esse desempenho é inferior a um décimo da solução Cysic SolarMSM (o cálculo de 2³⁰ MSM leva menos de 1 segundo).

Rolagem

Rolagem foi pesquisado internamente para aceleração baseada em GPU. Ao mesmo tempo, a Scroll e algumas instituições acadêmicas estão cooperando para explorar melhores soluções, e os resultados de suas pesquisas acadêmicas mais recentes foram publicados na ASPLOS 2023, a principal conferência na área de arquitetura de computadores [3]. Como projeto zkEVM líder, vale a pena aguardar e acompanhar o progresso de seu acompanhamento.

Referências

[1] PipeZK: Acelerando a prova de conhecimento zero com uma arquitetura em pipeline, ZhangYe [2] Aceleração FPGA de multiplicação multiescalar: CycloneMSM, JumpCrypto [3] GZKP: um sistema de prova de conhecimento zero acelerado por GPUAVISO LEGAL: As informações neste site são fornecidas como comentários gerais do mercado e não constituem aconselhamento de investimento. Nós encorajamos você a fazer sua própria pesquisa antes de investir.

Junte-se a nós para acompanhar as novidades: https://linktr.ee/coincu

Harold

coincu Novidades